applying 4 more jobs

This commit is contained in:

parent

c57a8984c4

commit

3f280fc0b3

9

.gitignore

vendored

Normal file

9

.gitignore

vendored

Normal file

@ -0,0 +1,9 @@

|

||||

# the CSVs of all my parts are ommitted, since I bought some parts that were wrong. I will draft up an official parts list later, or you can ask me now at brettsweiland@gmail.com.

|

||||

programmer_fix/

|

||||

stm32card_first.csv

|

||||

**/.gdbhistory*/

|

||||

v1_output/

|

||||

kicad/stm32card/stm32card-backups/*

|

||||

LCSC_Quote_Exported__20250213_081540.csv

|

||||

3dprint_tests/

|

||||

**/build/*

|

||||

49

README.md

49

README.md

@ -1,10 +1,41 @@

|

||||

# STM32 Buisnesscard Manelbrot Explorer

|

||||

## Waiting on PCBs for first prototype!

|

||||

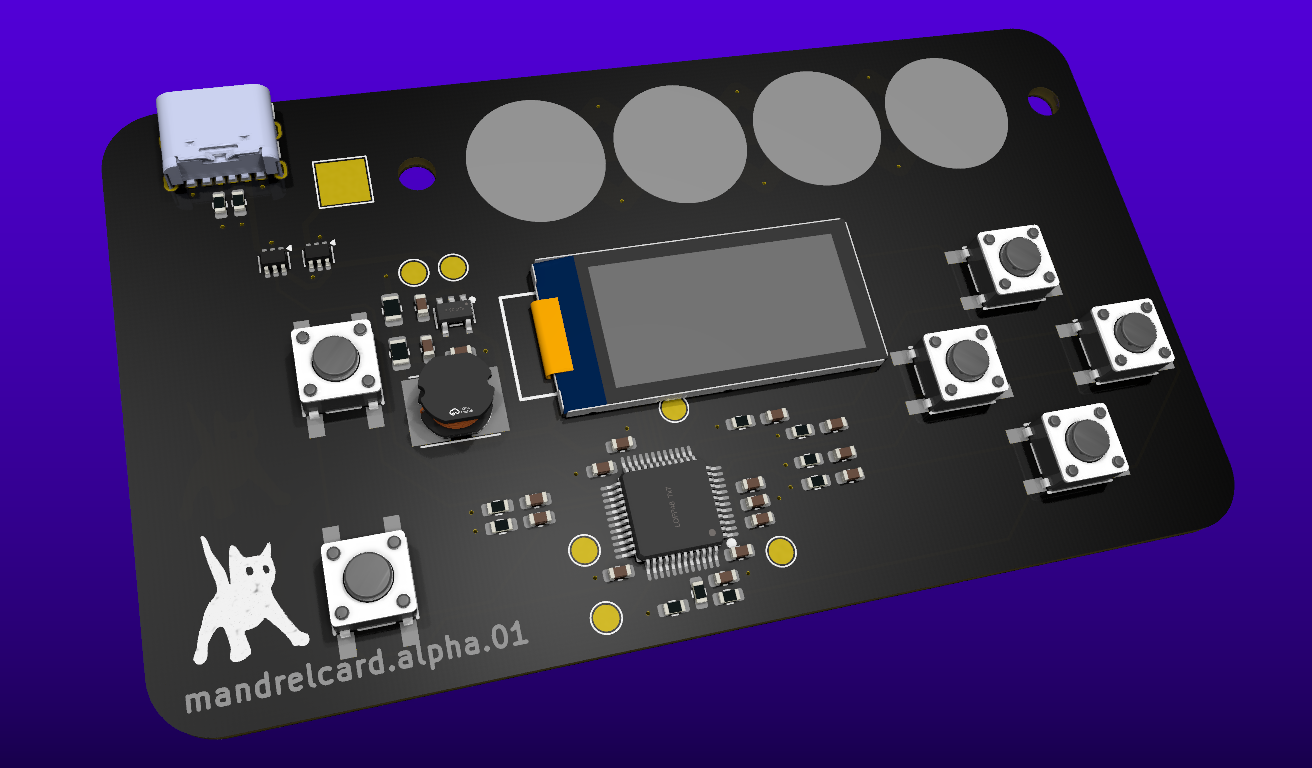

# STM32 Business card Mandelbrot Explorer

|

||||

A battery powered business card that can explore the Mandelbrot set. Meant to be cheaply made for handing out. Will likely include a flappy bird clone to encourage recruiter competition.

|

||||

# The first prototype works (pictures to be uploaded soon). Program in development! See below for a brief write up.

|

||||

|

||||

## This project is actively in progress!

|

||||

## Description

|

||||

This card will be powered by 4 zink air batteries (cost effective & high enough discharge) and will allow exploration of the mandelbrot fractal. Cost per card is projected to be about 7$, although I'm spending a lot more money learning.

|

||||

A cheaper MCU could be used, but I decided to go with something that has a developed ecosystem to save time. If you'd like to see software built from the ground up, without any HAL, see my wristwatch project.

|

||||

## Directories

|

||||

The recon folder are just some experiments I ran to get familiar with STM32.

|

||||

I've finished the schematic (see kicad folder), I'm now working on the PCB. It will likely be finished after the career fair.

|

||||

|

||||

## Project structure

|

||||

Code: [program/stm32f1_buisnesscard_v1/Core](https://git.bpcspace.com/indigo/stm32_business_card/program/stm32f1_buisnesscard_v1/Core])

|

||||

PCB: [kicad/](https://git.bpcspace.com/indigo/stm32_business_card/src/branch/main/kicad)

|

||||

|

||||

|

||||

## Software Development

|

||||

The software is currently working, but is more a proof of concept (messy and unoptimized). In it's current state, I'm leaning heavily on ST's HAL to save time. For a project where everything is written from the ground up, see my other projects below [^1]!

|

||||

|

||||

### Display

|

||||

I've modified [this repository](https://github.com/afiskon/stm32-st7735) to fit my needs. I've had to make some minor changes to utilize the ST7735's sleep mode, and to make the code work for my specific display. I expect I'll need to rewrite the library to manipulate raw registers to optimize SPI communication, as it currently uses HAL and is *very* slow. I'm considering implementing a game as well, which may require I access SPI via DMA.

|

||||

### FPU

|

||||

The STM32F1 lineup doesn't have an FPU, thus fixed point integer arithmetic is used to speed up rendering. The decimal is intentionally too close to the MSB, as this introduces aesthetic visual artifacts at no cost that I think are a nice twist.

|

||||

### MCU Power Consumption

|

||||

The software is interrupt based, saving power any time there's not an active job. After 30 seconds, a MOSFET will turn off the backlight and the MCU will in a deeper sleep state, where only a few microamps are consumed. This allows the card to operate without a power switch, as theoretically the sleeping power consumption is insignificant compared to the shelf life of these batteries (a few months).

|

||||

|

||||

## Hardware Development

|

||||

The PCB works, and is what I'm using to test code. I'm planning on making some changes, including adding MOSFETS for the display backlight and creating some art for the silk screen.

|

||||

The hardware is intentionally left simple for rapid development; there's two ideal diodes, allowing power delivery via USB-C or batteries, a step-down switching regulator, buttons with debouncing circuits, and of course, the MCU.

|

||||

Some of the most vital components are described below.

|

||||

|

||||

### Batteries

|

||||

This card will be powered by 4 zinc air batteries (cost effective & high power density, commonly used in hearing aids). The downside to these batteries is that they're non-rechargeable, and after activation, they only have a shelf life of a few weeks. Batteries are expensive, and what I've got is more then enough- it may actually be overkill.

|

||||

A battery holder was developed to be used with springs to hold the batteries in place. I haven't ordered the batteries yet, so I have yet to see how it performs.

|

||||

|

||||

### Display

|

||||

The display is the cheapest 2$ 65k 160x80 color LCD I could find on LCSC. It is the most expensive part of my card, matched with batteries. I'm sure I could have found it on Ali Express for 50¢, but hindsight is 20/20. It's actually very pretty, and I plan to upload images soon.

|

||||

|

||||

### SPI troubles

|

||||

Currently, SPI only works consistently at 4mHZ. I have yet to probe it with my oscilloscope and figure out what's wrong; I'm guessing parasitic capacitance. My next PCB will have differential routing to allow higher speeds.

|

||||

|

||||

## Things I'd change

|

||||

I'm used to working with a lot lower spec MCUs, and after the purchase I've found that the price of the STM32f1 is actually quite expensive for it's performance. I might want to try something uber cheap for my next project requiring a higher speed 32 bit processor, as long as it's got a HAL to accelerate development. The ch32v003 looks pretty cool...

|

||||

|

||||

## Other Projects

|

||||

[^1]: For another embedded project without any assistance from HAL, check out my (unfinished) [AVR wristwatch](https://git.bpcspace.com/indigo/AVRwristwatch), where everything- from the I2C display and RTC clock is developed from the ground up!

|

||||

For a much larger project that's not exactly embedded, check out my [Operating System](https://git.bpcspace.com/indigo/IndigoOS). I haven't been able to work on it since going to Missouri S&T, but some impressive feats include a bootloader, an efficient binary tree/buddy system physical memory allocator, and multi-core execution. It's a lot of code, maybe check it out!

|

||||

|

||||

BIN

datasheets/ST7735S.pdf

Normal file

BIN

datasheets/ST7735S.pdf

Normal file

Binary file not shown.

BIN

datasheets/STM32F103C8T6.pdf

Normal file

BIN

datasheets/STM32F103C8T6.pdf

Normal file

Binary file not shown.

BIN

datasheets/screen.pdf

Normal file

BIN

datasheets/screen.pdf

Normal file

Binary file not shown.

BIN

datasheets/stm32f1_ref.pdf

Normal file

BIN

datasheets/stm32f1_ref.pdf

Normal file

Binary file not shown.

BIN

imgs/kibby_loading.xcf

Normal file

BIN

imgs/kibby_loading.xcf

Normal file

Binary file not shown.

BIN

imgs/kibby_uncropped.jpg

Normal file

BIN

imgs/kibby_uncropped.jpg

Normal file

Binary file not shown.

|

After Width: | Height: | Size: 29 KiB |

File diff suppressed because it is too large

Load Diff

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

Binary file not shown.

@ -109,7 +109,6 @@

|

||||

(psnegative no)

|

||||

(psa4output no)

|

||||

(plot_black_and_white yes)

|

||||

(plotinvisibletext no)

|

||||

(sketchpadsonfab no)

|

||||

(plotpadnumbers no)

|

||||

(hidednponfab no)

|

||||

@ -7785,432 +7784,432 @@

|

||||

)

|

||||

)

|

||||

)

|

||||

(pad "1" smd oval

|

||||

(at -2.75 4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "1" smd rect

|

||||

(at -2.75 4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 3 "Net-(U4-VBAT)")

|

||||

(pinfunction "VBAT")

|

||||

(pintype "unspecified")

|

||||

(uuid "e79ab2a6-1796-442f-88fa-db289bfa48a0")

|

||||

)

|

||||

(pad "2" smd oval

|

||||

(at -2.25 4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "2" smd rect

|

||||

(at -2.25 4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 26 "unconnected-(U4-PC13-TAMPER-RTC-Pad2)")

|

||||

(pinfunction "PC13-TAMPER-RTC")

|

||||

(pintype "unspecified")

|

||||

(uuid "1a05e960-2a55-4f71-b147-e96e8a89e0fe")

|

||||

)

|

||||

(pad "3" smd oval

|

||||

(at -1.75 4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "3" smd rect

|

||||

(at -1.75 4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 30 "unconnected-(U4-PC14-OSC32_IN-Pad3)")

|

||||

(pinfunction "PC14-OSC32_IN")

|

||||

(pintype "unspecified")

|

||||

(uuid "73b6275e-19b3-4779-96c5-1a245d7144ce")

|

||||

)

|

||||

(pad "4" smd oval

|

||||

(at -1.25 4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "4" smd rect

|

||||

(at -1.25 4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 28 "unconnected-(U4-PC15-OSC32_OUT-Pad4)")

|

||||

(pinfunction "PC15-OSC32_OUT")

|

||||

(pintype "unspecified")

|

||||

(uuid "28b47442-9173-4d4f-a2fb-2b1653c691f1")

|

||||

)

|

||||

(pad "5" smd oval

|

||||

(at -0.75 4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "5" smd rect

|

||||

(at -0.75 4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 43 "unconnected-(U4-PD0-OSC_IN-Pad5)")

|

||||

(pinfunction "PD0-OSC_IN")

|

||||

(pintype "unspecified")

|

||||

(uuid "ab0b34da-d5ed-424f-a8ab-9a02141a4969")

|

||||

)

|

||||

(pad "6" smd oval

|

||||

(at -0.25 4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "6" smd rect

|

||||

(at -0.25 4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 31 "unconnected-(U4-PD1-OSC_OUT-Pad6)")

|

||||

(pinfunction "PD1-OSC_OUT")

|

||||

(pintype "unspecified")

|

||||

(uuid "77f01d04-c1c5-45e0-81bb-046fdd98ae5c")

|

||||

)

|

||||

(pad "7" smd oval

|

||||

(at 0.25 4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "7" smd rect

|

||||

(at 0.25 4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 59 "Net-(U4-NRST)")

|

||||

(pinfunction "NRST")

|

||||

(pintype "unspecified")

|

||||

(uuid "dcac7642-6b3d-43a7-997d-f00a139d4ab0")

|

||||

)

|

||||

(pad "8" smd oval

|

||||

(at 0.75 4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "8" smd rect

|

||||

(at 0.75 4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 1 "GND")

|

||||

(pinfunction "VSSA")

|

||||

(pintype "unspecified")

|

||||

(uuid "75228e14-830c-407e-9e11-f0ea5a14b10d")

|

||||

)

|

||||

(pad "9" smd oval

|

||||

(at 1.25 4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "9" smd rect

|

||||

(at 1.25 4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 2 "+3V0")

|

||||

(pinfunction "VDDA")

|

||||

(pintype "unspecified")

|

||||

(uuid "9d9f523d-8b64-49b3-a65e-4785152cb0b3")

|

||||

)

|

||||

(pad "10" smd oval

|

||||

(at 1.75 4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "10" smd rect

|

||||

(at 1.75 4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 14 "in_button_down")

|

||||

(pinfunction "PA0-WKUP")

|

||||

(pintype "unspecified")

|

||||

(uuid "9038ef2a-c022-477d-a7af-2aed110664bf")

|

||||

)

|

||||

(pad "11" smd oval

|

||||

(at 2.25 4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "11" smd rect

|

||||

(at 2.25 4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 16 "in_button_right")

|

||||

(pinfunction "PA1")

|

||||

(pintype "unspecified")

|

||||

(uuid "9bd2c635-b737-4f46-b335-6872129d0bb1")

|

||||

)

|

||||

(pad "12" smd oval

|

||||

(at 2.75 4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "12" smd rect

|

||||

(at 2.75 4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 15 "in_button_left")

|

||||

(pinfunction "PA2")

|

||||

(pintype "unspecified")

|

||||

(uuid "810a7c66-5c51-4218-ab71-ba62e41fb87d")

|

||||

)

|

||||

(pad "13" smd oval

|

||||

(at 4.25 2.75 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "13" smd rect

|

||||

(at 4.1 2.75 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 17 "in_button_up")

|

||||

(pinfunction "PA3")

|

||||

(pintype "unspecified")

|

||||

(uuid "8a779d3e-67f8-48c5-987a-4f051bf7d321")

|

||||

)

|

||||

(pad "14" smd oval

|

||||

(at 4.25 2.25 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "14" smd rect

|

||||

(at 4.1 2.25 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 34 "unconnected-(U4-PA4-Pad14)")

|

||||

(pinfunction "PA4")

|

||||

(pintype "unspecified")

|

||||

(uuid "92a65f03-7ad3-42e5-af53-52602856aa1c")

|

||||

)

|

||||

(pad "15" smd oval

|

||||

(at 4.25 1.75 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "15" smd rect

|

||||

(at 4.1 1.75 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 20 "spi1_sck")

|

||||

(pinfunction "PA5")

|

||||

(pintype "unspecified")

|

||||

(uuid "32e2cd59-1a1a-4a60-84a0-d576940aad30")

|

||||

)

|

||||

(pad "16" smd oval

|

||||

(at 4.25 1.25 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "16" smd rect

|

||||

(at 4.1 1.25 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 49 "spi1_miso")

|

||||

(pinfunction "PA6")

|

||||

(pintype "unspecified")

|

||||

(uuid "fdbb6c52-95a6-4fde-82f2-47adf573ec4a")

|

||||

)

|

||||

(pad "17" smd oval

|

||||

(at 4.25 0.75 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "17" smd rect

|

||||

(at 4.1 0.75 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 22 "spi1_mosi")

|

||||

(pinfunction "PA7")

|

||||

(pintype "unspecified")

|

||||

(uuid "e792b8c6-90a2-4926-ba45-e0cba4cabc42")

|

||||

)

|

||||

(pad "18" smd oval

|

||||

(at 4.25 0.25 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "18" smd rect

|

||||

(at 4.1 0.25 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 53 "lcd_dataselect")

|

||||

(pinfunction "PB0")

|

||||

(pintype "unspecified")

|

||||

(uuid "9f744027-3ace-4393-99a0-b336b4d81503")

|

||||

)

|

||||

(pad "19" smd oval

|

||||

(at 4.25 -0.25 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "19" smd rect

|

||||

(at 4.1 -0.25 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 33 "lcd_reset")

|

||||

(pinfunction "PB1")

|

||||

(pintype "unspecified")

|

||||

(uuid "566d4e9c-be81-4101-898b-e5c6d19a406d")

|

||||

)

|

||||

(pad "20" smd oval

|

||||

(at 4.25 -0.75 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "20" smd rect

|

||||

(at 4.1 -0.75 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 55 "lcd_cs")

|

||||

(pinfunction "PB2")

|

||||

(pintype "unspecified")

|

||||

(uuid "e3c72a81-422c-4a4e-bfd8-52c744114e68")

|

||||

)

|

||||

(pad "21" smd oval

|

||||

(at 4.25 -1.25 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "21" smd rect

|

||||

(at 4.1 -1.25 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 32 "unconnected-(U4-PB10-Pad21)")

|

||||

(pinfunction "PB10")

|

||||

(pintype "unspecified")

|

||||

(uuid "7e9823b4-5e4f-4346-bd89-f93d913a0470")

|

||||

)

|

||||

(pad "22" smd oval

|

||||

(at 4.25 -1.75 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "22" smd rect

|

||||

(at 4.1 -1.75 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 40 "unconnected-(U4-PB11-Pad22)")

|

||||

(pinfunction "PB11")

|

||||

(pintype "unspecified")

|

||||

(uuid "939d3526-f560-48ea-afb8-980d166c0254")

|

||||

)

|

||||

(pad "23" smd oval

|

||||

(at 4.25 -2.25 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "23" smd rect

|

||||

(at 4.1 -2.25 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 1 "GND")

|

||||

(pinfunction "VSS_1")

|

||||

(pintype "unspecified")

|

||||

(uuid "7440ebae-93d6-4309-bb3a-bbcf01e45ad4")

|

||||

)

|

||||

(pad "24" smd oval

|

||||

(at 4.25 -2.75 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "24" smd rect

|

||||

(at 4.1 -2.75 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 2 "+3V0")

|

||||

(pinfunction "VDD_1")

|

||||

(pintype "unspecified")

|

||||

(uuid "d82a8937-2e8a-4bb7-9f80-a9b84b9e8f52")

|

||||

)

|

||||

(pad "25" smd oval

|

||||

(at 2.75 -4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "25" smd rect

|

||||

(at 2.75 -4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 25 "power_info")

|

||||

(pinfunction "PB12")

|

||||

(pintype "unspecified")

|

||||

(uuid "1294e193-e0ff-4292-b140-594a112ae602")

|

||||

)

|

||||

(pad "26" smd oval

|

||||

(at 2.25 -4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "26" smd rect

|

||||

(at 2.25 -4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 11 "in_button_a")

|

||||

(pinfunction "PB13")

|

||||

(pintype "unspecified")

|

||||

(uuid "218f6e51-f6a2-4547-9719-ff66b2109f2f")

|

||||

)

|

||||

(pad "27" smd oval

|

||||

(at 1.75 -4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "27" smd rect

|

||||

(at 1.75 -4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 13 "in_button_b")

|

||||

(pinfunction "PB14")

|

||||

(pintype "unspecified")

|

||||

(uuid "b43c9964-3dd0-40e5-a924-4e4afa1a0acf")

|

||||

)

|

||||

(pad "28" smd oval

|

||||

(at 1.25 -4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "28" smd rect

|

||||

(at 1.25 -4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 42 "unconnected-(U4-PB15-Pad28)")

|

||||

(pinfunction "PB15")

|

||||

(pintype "unspecified")

|

||||

(uuid "a069a5f1-68ad-46ff-86b9-7595c6f139b6")

|

||||

)

|

||||

(pad "29" smd oval

|

||||

(at 0.75 -4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "29" smd rect

|

||||

(at 0.75 -4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 36 "unconnected-(U4-PA8-Pad29)")

|

||||

(pinfunction "PA8")

|

||||

(pintype "unspecified")

|

||||

(uuid "8ce0a254-6994-4377-9224-16722c7801b8")

|

||||

)

|

||||

(pad "30" smd oval

|

||||

(at 0.25 -4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "30" smd rect

|

||||

(at 0.25 -4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 46 "unconnected-(U4-PA9-Pad30)")

|

||||

(pinfunction "PA9")

|

||||

(pintype "unspecified")

|

||||

(uuid "d3ebe670-7847-4127-b5c4-19f171eb81c9")

|

||||

)

|

||||

(pad "31" smd oval

|

||||

(at -0.25 -4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "31" smd rect

|

||||

(at -0.25 -4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 35 "unconnected-(U4-PA10-Pad31)")

|

||||

(pinfunction "PA10")

|

||||

(pintype "unspecified")

|

||||

(uuid "8b8da939-4024-4e32-96e4-fc5543e3e18f")

|

||||

)

|

||||

(pad "32" smd oval

|

||||

(at -0.75 -4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "32" smd rect

|

||||

(at -0.75 -4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 48 "unconnected-(U4-PA11-Pad32)")

|

||||

(pinfunction "PA11")

|

||||

(pintype "unspecified")

|

||||

(uuid "dd72a79a-5424-43d2-ac5b-4cf6f1255fdf")

|

||||

)

|

||||

(pad "33" smd oval

|

||||

(at -1.25 -4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "33" smd rect

|

||||

(at -1.25 -4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 38 "unconnected-(U4-PA12-Pad33)")

|

||||

(pinfunction "PA12")

|

||||

(pintype "unspecified")

|

||||

(uuid "91063092-82f4-400e-843e-698551e2e924")

|

||||

)

|

||||

(pad "34" smd oval

|

||||

(at -1.75 -4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "34" smd rect

|

||||

(at -1.75 -4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 61 "Net-(U4-PA13)")

|

||||

(pinfunction "PA13")

|

||||

(pintype "unspecified")

|

||||

(uuid "c2b2b7fd-8da9-43c3-8295-385616c36888")

|

||||

)

|

||||

(pad "35" smd oval

|

||||

(at -2.25 -4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "35" smd rect

|

||||

(at -2.25 -4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 1 "GND")

|

||||

(pinfunction "VSS_2")

|

||||

(pintype "unspecified")

|

||||

(uuid "24317dc7-634e-4222-9310-d4bc9f967cb0")

|

||||

)

|

||||

(pad "36" smd oval

|

||||

(at -2.75 -4.25 90)

|

||||

(size 0.27 1.5)

|

||||

(pad "36" smd rect

|

||||

(at -2.75 -4.1 90)

|

||||

(size 0.27 1.2)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 2 "+3V0")

|

||||

(pinfunction "VDD_2")

|

||||

(pintype "unspecified")

|

||||

(uuid "e8ed6ff4-de5a-4f85-a401-8ebfda5f8f0f")

|

||||

)

|

||||

(pad "37" smd oval

|

||||

(at -4.25 -2.75 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "37" smd rect

|

||||

(at -4.1 -2.75 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 60 "Net-(U4-PA14)")

|

||||

(pinfunction "PA14")

|

||||

(pintype "unspecified")

|

||||

(uuid "1f55ad4f-182f-47cf-8b85-346142f98316")

|

||||

)

|

||||

(pad "38" smd oval

|

||||

(at -4.25 -2.25 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "38" smd rect

|

||||

(at -4.1 -2.25 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 29 "unconnected-(U4-PA15-Pad38)")

|

||||

(pinfunction "PA15")

|

||||

(pintype "unspecified")

|

||||

(uuid "677e4bfa-e584-4c60-a5d8-fd2f7affc275")

|

||||

)

|

||||

(pad "39" smd oval

|

||||

(at -4.25 -1.75 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "39" smd rect

|

||||

(at -4.1 -1.75 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 41 "unconnected-(U4-PB3-Pad39)")

|

||||

(pinfunction "PB3")

|

||||

(pintype "unspecified")

|

||||

(uuid "a922c2b2-2a9f-481b-8b51-9ce0bd8c5516")

|

||||

)

|

||||

(pad "40" smd oval

|

||||

(at -4.25 -1.25 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "40" smd rect

|

||||

(at -4.1 -1.25 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 44 "unconnected-(U4-PB4-Pad40)")

|

||||

(pinfunction "PB4")

|

||||

(pintype "unspecified")

|

||||

(uuid "e2c35414-4f6d-4fc0-810b-348e9a9ad944")

|

||||

)

|

||||

(pad "41" smd oval

|

||||

(at -4.25 -0.75 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "41" smd rect

|

||||

(at -4.1 -0.75 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 27 "unconnected-(U4-PB5-Pad41)")

|

||||

(pinfunction "PB5")

|

||||

(pintype "unspecified")

|

||||

(uuid "21cc3b59-48b9-4a5b-8d0e-038d18defcfd")

|

||||

)

|

||||

(pad "42" smd oval

|

||||

(at -4.25 -0.25 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "42" smd rect

|

||||

(at -4.1 -0.25 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 52 "unconnected-(U4-PB6-Pad42)")

|

||||

(pinfunction "PB6")

|

||||

(pintype "unspecified")

|

||||

(uuid "c4edd4f7-b058-4939-af04-b85f06692d7e")

|

||||

)

|

||||

(pad "43" smd oval

|

||||

(at -4.25 0.25 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "43" smd rect

|

||||

(at -4.1 0.25 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 37 "unconnected-(U4-PB7-Pad43)")

|

||||

(pinfunction "PB7")

|

||||

(pintype "unspecified")

|

||||

(uuid "7da691e2-6a88-420a-bb2d-69849698cf32")

|

||||

)

|

||||

(pad "44" smd oval

|

||||

(at -4.25 0.75 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "44" smd rect

|

||||

(at -4.1 0.75 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 12 "Net-(U4-BOOT0)")

|

||||

(pinfunction "BOOT0")

|

||||

(pintype "unspecified")

|

||||

(uuid "1c05f1dd-5aea-4c70-8aa3-fb41e5f52f8e")

|

||||

)

|

||||

(pad "45" smd oval

|

||||

(at -4.25 1.25 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "45" smd rect

|

||||

(at -4.1 1.25 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 54 "unconnected-(U4-PB8-Pad45)")

|

||||

(pinfunction "PB8")

|

||||

(pintype "unspecified")

|

||||

(uuid "a448b535-f251-490e-81b3-6788b9f23dec")

|

||||

)

|

||||

(pad "46" smd oval

|

||||

(at -4.25 1.75 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "46" smd rect

|

||||

(at -4.1 1.75 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 47 "unconnected-(U4-PB9-Pad46)")

|

||||

(pinfunction "PB9")

|

||||

(pintype "unspecified")

|

||||

(uuid "d6136b25-93e2-4c71-a1c1-59cce16df0a7")

|

||||

)

|

||||

(pad "47" smd oval

|

||||

(at -4.25 2.25 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "47" smd rect

|

||||

(at -4.1 2.25 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 1 "GND")

|

||||

(pinfunction "VSS_3")

|

||||

(pintype "unspecified")

|

||||

(uuid "6b6a454c-46d5-4148-817b-94b9f32762d4")

|

||||

)

|

||||

(pad "48" smd oval

|

||||

(at -4.25 2.75 90)

|

||||

(size 1.5 0.27)

|

||||

(pad "48" smd rect

|

||||

(at -4.1 2.75 90)

|

||||

(size 1.2 0.27)

|

||||

(layers "F.Cu" "F.Mask" "F.Paste")

|

||||

(net 2 "+3V0")

|

||||

(pinfunction "VDD_3")

|

||||

@ -24722,6 +24721,19 @@

|

||||

(justify left bottom)

|

||||

)

|

||||

)

|

||||

(gr_text "BEFORE RE-ORDERING:\n- fix routing to MCU; footprint was changed\n- fix vtext\n- SPI NSI\n- LEDs?\n- change your god damn test pins - remove if no more needed\n- remove button outlines\n- SPI speed stuck at 2mHZ - differential routing?\n- LCD backlight MOSFTER\n- test to see if sleep mode is accurate to datasheet - screen responds in sleep mode, which is sus\n- add mosfet to LED VDD if above is too sus"

|

||||

(at 135.087495 79.340705 0)

|

||||

(layer "Cmts.User" knockout)

|

||||

(uuid "f62f4e68-b57a-4b61-ac63-ac1136d71720")

|

||||

(effects

|

||||

(font

|

||||

(size 1.5 1.5)

|

||||

(thickness 0.3)

|

||||

(bold yes)

|

||||

)

|

||||

(justify left bottom)

|

||||

)

|

||||

)

|

||||

(segment

|

||||

(start 182.407094 90.00238)

|

||||

(end 187.403529 94.998815)

|

||||

@ -26572,11 +26584,11 @@

|

||||

)

|

||||

(segment

|

||||

(start 177.240878 120.284125)

|

||||

(end 176.240878 120.284125)

|

||||

(end 176.090878 120.284125)

|

||||

(width 0.25)

|

||||

(layer "F.Cu")

|

||||

(net 16)

|

||||

(uuid "efa4a209-6ef1-41c5-aac2-a1bbf3aa6436")

|

||||

(uuid "be0e08ba-2b96-42b8-80e0-f297a07d0120")

|

||||

)

|

||||

(segment

|

||||

(start 202.951133 109.165534)

|

||||

|

||||

@ -1,7 +1,7 @@

|

||||

{

|

||||

"board": {

|

||||

"active_layer": 0,

|

||||

"active_layer_preset": "Back Layers",

|

||||

"active_layer": 7,

|

||||

"active_layer_preset": "",

|

||||

"auto_track_width": true,

|

||||

"hidden_netclasses": [],

|

||||

"hidden_nets": [],

|

||||

@ -48,7 +48,7 @@

|

||||

"conflict_shadows",

|

||||

"shapes"

|

||||

],

|

||||

"visible_layers": "00000000_00000000_00000002_2200888c",

|

||||

"visible_layers": "00000000_00000000_00000008_82082223",

|

||||

"zone_display_mode": 1

|

||||

},

|

||||

"git": {

|

||||

|

||||

@ -108,6 +108,7 @@

|

||||

"solder_mask_bridge": "error",

|

||||

"starved_thermal": "error",

|

||||

"text_height": "warning",

|

||||

"text_on_edge_cuts": "error",

|

||||

"text_thickness": "warning",

|

||||

"through_hole_pad_without_hole": "error",

|

||||

"too_many_vias": "error",

|

||||

|

||||

1

kicad/stm32card/~_autosave-stm32card.kicad_pcb.lck

Normal file

1

kicad/stm32card/~_autosave-stm32card.kicad_pcb.lck

Normal file

@ -0,0 +1 @@

|

||||

{"hostname":"indigosDesktop","username":"indigo"}

|

||||

1

program/stm32-st7735

Submodule

1

program/stm32-st7735

Submodule

@ -0,0 +1 @@

|

||||

Subproject commit b9408107226246a8494e6a729dfaeebfa0a75a5d

|

||||

187

program/stm32f1_buisnesscard_v1/.gdb_history

Normal file

187

program/stm32f1_buisnesscard_v1/.gdb_history

Normal file

@ -0,0 +1,187 @@

|

||||

context

|

||||

file

|

||||

continue

|

||||

continue

|

||||

set exception-verbose on

|

||||

continue

|

||||

exit

|

||||

file

|

||||

quit

|

||||

quit

|

||||

context

|

||||

next

|

||||

quit

|

||||

nexti

|

||||

nexti

|

||||

continue

|

||||

nexti

|

||||

monitor reset halt

|

||||

context

|

||||

continue

|

||||

next

|

||||

next

|

||||

next

|

||||

next

|

||||

next

|

||||

load

|

||||

context

|

||||

nexti

|

||||

continue

|

||||

monitor reset halt

|

||||

set mem inaccessible-by-default off

|

||||

context

|

||||

load

|

||||

context

|

||||

nexti

|

||||

load

|

||||

context

|

||||

b main

|

||||

c

|

||||

load

|

||||

context

|

||||

nexti

|

||||

gdb memory_map enable

|

||||

exit()

|

||||

exit

|

||||

context

|

||||

start

|

||||

context

|

||||

quit

|

||||

target extended-remote | \

|

||||

openocd -c "gdb port pipe; log_output openocd.log"

|

||||

target extended-remote | openocd -c "gdb port pipe; log_output openocd.log"

|

||||

exit()

|

||||

exit

|

||||

quit

|

||||

target extended-remote localhost:3333

|

||||

monitor reset halt

|

||||

load

|

||||

context

|

||||

where

|

||||

list _stack_init

|

||||

list _stack_init()

|

||||

set_enable_virt2phys

|

||||

load

|

||||

b HAL_EXTI_RegisterCallback

|

||||

p 0x08000070

|

||||

p main

|

||||

nexti

|

||||

quit

|

||||

load

|

||||

context

|

||||

registers

|

||||

info reg

|

||||

show debug monitor

|

||||

show debug

|

||||

show debug monitor

|

||||

show debug arm

|

||||

set debug arm on

|

||||

show debug arm

|

||||

context

|

||||

nexti

|

||||

load

|

||||

info reg

|

||||

target sim

|

||||

monitor shutdown

|

||||

monitor shutdown

|

||||

exit

|

||||

file build/stm32f1_buisnesscard_v1.elf

|

||||

load

|

||||

monitor reset run

|

||||

exit

|

||||

quit

|

||||

nexti

|

||||

next

|

||||

nexti

|

||||

c

|

||||

nexti

|

||||

continue

|

||||

nexti

|

||||

c

|

||||

quit

|

||||

nexti

|

||||

next

|

||||

break main.c:120

|

||||

r

|

||||

break main.c:82

|

||||

c

|

||||

exit()

|

||||

quit

|

||||

c

|

||||

next

|

||||

quit

|

||||

load

|

||||

start

|

||||

quit

|

||||

start

|

||||

c

|

||||

target extended-remote | \

|

||||

openocd -c "gdb port pipe; log_output openocd.log"

|

||||

target extended-remote | openocd -c "gdb port pipe; log_output openocd.log"

|

||||

exit

|

||||

tar ext :3333

|

||||

b HAL_GPIO_EXTI_Callback

|

||||

b HAL_TIM_PeriodElapsedCallback

|

||||

load

|

||||

context

|

||||

c

|

||||

c

|

||||

print htim

|

||||

print *htim

|

||||

c

|

||||

tar ext :3333

|

||||

info b

|

||||

d b

|

||||

d

|

||||

d

|

||||

b HAL_TIM_PeriodElapsedCallback

|

||||

b HAL_GPIO_EXTI_Callback

|

||||

c

|

||||

c

|

||||

restart

|

||||

run

|

||||

c

|

||||

c

|

||||

quit

|

||||

hu

|

||||

hi

|

||||

quit

|

||||

quit

|

||||

quit

|

||||

quit

|

||||

quit

|

||||

exit

|

||||

exit

|

||||

quit

|

||||

exittar ext localhost 3333

|

||||

tar ext localhost 3333

|

||||

target extended-remote 3333

|

||||

target extended-remote localhost:3333

|

||||

exit

|

||||

quit

|

||||

quit

|

||||

quit

|

||||

b mandelbrot.c:102

|

||||

c

|

||||

c

|

||||

print cam

|

||||

c

|

||||

print cam

|

||||

c

|

||||

print cam

|

||||

step

|

||||

next

|

||||

next

|

||||

print i_offset

|

||||

print r_offset

|

||||

print *cam

|

||||

next

|

||||

print *cam

|

||||

next

|

||||

print cam

|

||||

print *cam

|

||||

next

|

||||

print cam

|

||||

c

|

||||

print cam

|

||||

quit

|

||||

25

program/stm32f1_buisnesscard_v1/.mxproject

Normal file

25

program/stm32f1_buisnesscard_v1/.mxproject

Normal file

@ -0,0 +1,25 @@

|

||||

[PreviousLibFiles]

|

||||

LibFiles=Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_spi.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_spi.h;Drivers/STM32F1xx_HAL_Driver/Inc/Legacy/stm32_hal_legacy.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_def.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_rcc.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_rcc_ex.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_bus.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_rcc.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_system.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_utils.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_gpio.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_gpio_ex.h;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_gpio_ex.c;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_gpio.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_dma_ex.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_dma.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_dma.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_cortex.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_cortex.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_pwr.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_pwr.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_flash.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_flash_ex.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_exti.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_exti.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_tim.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_tim.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_tim_ex.h;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_spi.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_rcc.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_rcc_ex.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_gpio.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_dma.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_cortex.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_pwr.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_flash.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_flash_ex.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_exti.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_tim.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_tim_ex.c;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_spi.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_spi.h;Drivers/STM32F1xx_HAL_Driver/Inc/Legacy/stm32_hal_legacy.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_def.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_rcc.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_rcc_ex.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_bus.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_rcc.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_system.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_utils.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_gpio.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_gpio_ex.h;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_gpio_ex.c;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_gpio.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_dma_ex.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_dma.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_dma.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_cortex.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_cortex.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_pwr.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_pwr.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_flash.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_flash_ex.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_exti.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_exti.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_tim.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_ll_tim.h;Drivers/STM32F1xx_HAL_Driver/Inc/stm32f1xx_hal_tim_ex.h;Drivers/CMSIS/Device/ST/STM32F1xx/Include/stm32f103xb.h;Drivers/CMSIS/Device/ST/STM32F1xx/Include/stm32f1xx.h;Drivers/CMSIS/Device/ST/STM32F1xx/Include/system_stm32f1xx.h;Drivers/CMSIS/Device/ST/STM32F1xx/Include/system_stm32f1xx.h;Drivers/CMSIS/Device/ST/STM32F1xx/Source/Templates/system_stm32f1xx.c;Drivers/CMSIS/Include/core_cm3.h;Drivers/CMSIS/Include/core_cm7.h;Drivers/CMSIS/Include/core_cm1.h;Drivers/CMSIS/Include/core_cm0plus.h;Drivers/CMSIS/Include/cmsis_armcc.h;Drivers/CMSIS/Include/cmsis_gcc.h;Drivers/CMSIS/Include/cmsis_version.h;Drivers/CMSIS/Include/core_armv8mbl.h;Drivers/CMSIS/Include/tz_context.h;Drivers/CMSIS/Include/core_cm23.h;Drivers/CMSIS/Include/core_armv8mml.h;Drivers/CMSIS/Include/cmsis_compiler.h;Drivers/CMSIS/Include/core_cm33.h;Drivers/CMSIS/Include/mpu_armv8.h;Drivers/CMSIS/Include/mpu_armv7.h;Drivers/CMSIS/Include/core_sc000.h;Drivers/CMSIS/Include/core_cm4.h;Drivers/CMSIS/Include/core_cm0.h;Drivers/CMSIS/Include/cmsis_iccarm.h;Drivers/CMSIS/Include/core_sc300.h;Drivers/CMSIS/Include/cmsis_armclang.h;

|

||||

|

||||

[PreviousUsedMakefileFiles]

|

||||

SourceFiles=Core/Src/main.c;Core/Src/stm32f1xx_it.c;Core/Src/stm32f1xx_hal_msp.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_gpio_ex.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_spi.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_rcc.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_rcc_ex.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_gpio.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_dma.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_cortex.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_pwr.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_flash.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_flash_ex.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_exti.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_tim.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_tim_ex.c;Drivers/CMSIS/Device/ST/STM32F1xx/Source/Templates/system_stm32f1xx.c;Core/Src/system_stm32f1xx.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_gpio_ex.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_spi.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_rcc.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_rcc_ex.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_gpio.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_dma.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_cortex.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_pwr.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_flash.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_flash_ex.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_exti.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_tim.c;Drivers/STM32F1xx_HAL_Driver/Src/stm32f1xx_hal_tim_ex.c;Drivers/CMSIS/Device/ST/STM32F1xx/Source/Templates/system_stm32f1xx.c;Core/Src/system_stm32f1xx.c;;;

|

||||

HeaderPath=Drivers/STM32F1xx_HAL_Driver/Inc;Drivers/STM32F1xx_HAL_Driver/Inc/Legacy;Drivers/CMSIS/Device/ST/STM32F1xx/Include;Drivers/CMSIS/Include;Core/Inc;

|

||||

CDefines=USE_HAL_DRIVER;STM32F103xB;USE_HAL_DRIVER;USE_HAL_DRIVER;

|

||||

|

||||

[PreviousGenFiles]

|

||||

AdvancedFolderStructure=true

|

||||

HeaderFileListSize=3

|

||||

HeaderFiles#0=../Core/Inc/stm32f1xx_it.h

|

||||

HeaderFiles#1=../Core/Inc/stm32f1xx_hal_conf.h

|

||||

HeaderFiles#2=../Core/Inc/main.h

|

||||

HeaderFolderListSize=1

|

||||

HeaderPath#0=../Core/Inc

|

||||

HeaderFiles=;

|

||||

SourceFileListSize=3

|

||||

SourceFiles#0=../Core/Src/stm32f1xx_it.c

|

||||

SourceFiles#1=../Core/Src/stm32f1xx_hal_msp.c

|

||||

SourceFiles#2=../Core/Src/main.c

|

||||

SourceFolderListSize=1

|

||||

SourcePath#0=../Core/Src

|

||||

SourceFiles=;

|

||||

|

||||

1

program/stm32f1_buisnesscard_v1/Core/Inc/fonts.h

Symbolic link

1

program/stm32f1_buisnesscard_v1/Core/Inc/fonts.h

Symbolic link

@ -0,0 +1 @@

|

||||

../../../stm32-st7735/st7735/fonts.h

|

||||

@ -27,7 +27,7 @@ extern "C" {

|

||||

#endif

|

||||

|

||||

/* Includes ------------------------------------------------------------------*/

|

||||

#include "stm32l4xx_hal.h"

|

||||

#include "stm32f1xx_hal.h"

|

||||

|

||||

/* Private includes ----------------------------------------------------------*/

|

||||

/* USER CODE BEGIN Includes */

|

||||

@ -57,30 +57,6 @@ void Error_Handler(void);

|

||||

/* USER CODE END EFP */

|

||||

|

||||

/* Private defines -----------------------------------------------------------*/

|

||||

#define B1_Pin GPIO_PIN_13

|

||||

#define B1_GPIO_Port GPIOC

|

||||

#define MCO_Pin GPIO_PIN_0

|

||||

#define MCO_GPIO_Port GPIOH

|

||||

#define USART_TX_Pin GPIO_PIN_2

|

||||

#define USART_TX_GPIO_Port GPIOA

|

||||

#define USART_RX_Pin GPIO_PIN_3

|

||||

#define USART_RX_GPIO_Port GPIOA

|

||||

#define SMPS_EN_Pin GPIO_PIN_4

|

||||

#define SMPS_EN_GPIO_Port GPIOA

|

||||

#define SMPS_V1_Pin GPIO_PIN_5

|

||||

#define SMPS_V1_GPIO_Port GPIOA

|

||||

#define SMPS_PG_Pin GPIO_PIN_6

|

||||

#define SMPS_PG_GPIO_Port GPIOA

|

||||

#define SMPS_SW_Pin GPIO_PIN_7

|

||||

#define SMPS_SW_GPIO_Port GPIOA

|

||||

#define LD4_Pin GPIO_PIN_13

|

||||

#define LD4_GPIO_Port GPIOB

|

||||

#define TMS_Pin GPIO_PIN_13

|

||||

#define TMS_GPIO_Port GPIOA

|

||||

#define TCK_Pin GPIO_PIN_14

|

||||

#define TCK_GPIO_Port GPIOA

|

||||

#define SWO_Pin GPIO_PIN_3

|

||||

#define SWO_GPIO_Port GPIOB

|

||||

|

||||

/* USER CODE BEGIN Private defines */

|

||||

|

||||

24

program/stm32f1_buisnesscard_v1/Core/Inc/mandelbrot.h

Normal file

24

program/stm32f1_buisnesscard_v1/Core/Inc/mandelbrot.h

Normal file

@ -0,0 +1,24 @@

|

||||

#pragma once

|

||||

|

||||

extern int state;

|

||||

enum states {

|

||||

MANDELBROT,

|

||||

BURNINGSHIP,

|

||||

SCREENSAVER,

|

||||

HELP,

|

||||

};

|

||||

|

||||

void draw_mandelbrot(int key_pressed);

|

||||

/** the interrupt handler should read the pin pressed, then translate it into one of these.

|

||||

* Ensures that if we have to change pins, adjustments are easy.

|

||||

*/

|

||||

enum buttons {

|

||||

KEYCODE_UP,

|

||||

KEYCODE_RIGHT,

|

||||

KEYCODE_DOWN,

|

||||

KEYCODE_LEFT,

|

||||

KEYCODE_A,

|

||||

KEYCODE_B,

|

||||

//we need to call the function once during boot

|

||||

KEYCODE_NONE = 0xff

|

||||

};

|

||||

1

program/stm32f1_buisnesscard_v1/Core/Inc/st7735.h

Symbolic link

1

program/stm32f1_buisnesscard_v1/Core/Inc/st7735.h

Symbolic link

@ -0,0 +1 @@

|

||||

../../../stm32-st7735/st7735/st7735.h

|

||||

391

program/stm32f1_buisnesscard_v1/Core/Inc/stm32f1xx_hal_conf.h

Normal file

391

program/stm32f1_buisnesscard_v1/Core/Inc/stm32f1xx_hal_conf.h

Normal file

@ -0,0 +1,391 @@

|

||||

/* USER CODE BEGIN Header */

|

||||

/**

|

||||

******************************************************************************

|

||||

* @file stm32f1xx_hal_conf.h

|

||||

* @brief HAL configuration file.

|

||||

******************************************************************************

|

||||

* @attention

|

||||

*

|

||||

* Copyright (c) 2017 STMicroelectronics.

|

||||

* All rights reserved.

|

||||

*

|

||||

* This software is licensed under terms that can be found in the LICENSE file

|

||||

* in the root directory of this software component.

|

||||

* If no LICENSE file comes with this software, it is provided AS-IS.

|

||||

*

|

||||

******************************************************************************

|

||||

*/

|

||||

/* USER CODE END Header */

|

||||

|

||||

/* Define to prevent recursive inclusion -------------------------------------*/

|

||||

#ifndef __STM32F1xx_HAL_CONF_H

|

||||

#define __STM32F1xx_HAL_CONF_H

|

||||

|

||||

#ifdef __cplusplus

|

||||

extern "C" {

|

||||

#endif

|

||||

|

||||

/* Exported types ------------------------------------------------------------*/

|

||||

/* Exported constants --------------------------------------------------------*/

|

||||

|

||||

/* ########################## Module Selection ############################## */

|

||||

/**

|

||||

* @brief This is the list of modules to be used in the HAL driver

|

||||

*/

|

||||

|

||||

#define HAL_MODULE_ENABLED

|

||||

/*#define HAL_ADC_MODULE_ENABLED */

|

||||

/*#define HAL_CRYP_MODULE_ENABLED */

|

||||

/*#define HAL_CAN_MODULE_ENABLED */

|

||||

/*#define HAL_CAN_LEGACY_MODULE_ENABLED */

|

||||

/*#define HAL_CEC_MODULE_ENABLED */

|

||||

/*#define HAL_CORTEX_MODULE_ENABLED */

|

||||

/*#define HAL_CRC_MODULE_ENABLED */

|

||||

/*#define HAL_DAC_MODULE_ENABLED */

|

||||

/*#define HAL_DMA_MODULE_ENABLED */

|

||||

/*#define HAL_ETH_MODULE_ENABLED */

|

||||

/*#define HAL_FLASH_MODULE_ENABLED */

|

||||

#define HAL_GPIO_MODULE_ENABLED

|

||||

/*#define HAL_I2C_MODULE_ENABLED */

|

||||

/*#define HAL_I2S_MODULE_ENABLED */

|

||||

/*#define HAL_IRDA_MODULE_ENABLED */

|

||||

/*#define HAL_IWDG_MODULE_ENABLED */

|

||||

/*#define HAL_NOR_MODULE_ENABLED */

|

||||

/*#define HAL_NAND_MODULE_ENABLED */

|

||||

/*#define HAL_PCCARD_MODULE_ENABLED */

|

||||

/*#define HAL_PCD_MODULE_ENABLED */

|

||||

/*#define HAL_HCD_MODULE_ENABLED */

|

||||

/*#define HAL_PWR_MODULE_ENABLED */

|

||||

/*#define HAL_RCC_MODULE_ENABLED */

|

||||

/*#define HAL_RTC_MODULE_ENABLED */

|

||||

/*#define HAL_SD_MODULE_ENABLED */

|

||||

/*#define HAL_MMC_MODULE_ENABLED */

|

||||

/*#define HAL_SDRAM_MODULE_ENABLED */

|

||||

/*#define HAL_SMARTCARD_MODULE_ENABLED */

|

||||

#define HAL_SPI_MODULE_ENABLED

|

||||

/*#define HAL_SRAM_MODULE_ENABLED */

|

||||

#define HAL_TIM_MODULE_ENABLED

|

||||

/*#define HAL_UART_MODULE_ENABLED */

|

||||

/*#define HAL_USART_MODULE_ENABLED */

|

||||

/*#define HAL_WWDG_MODULE_ENABLED */

|

||||

|

||||

#define HAL_CORTEX_MODULE_ENABLED

|

||||

#define HAL_DMA_MODULE_ENABLED

|

||||

#define HAL_FLASH_MODULE_ENABLED

|

||||

#define HAL_EXTI_MODULE_ENABLED

|

||||

#define HAL_GPIO_MODULE_ENABLED

|

||||

#define HAL_PWR_MODULE_ENABLED

|

||||

#define HAL_RCC_MODULE_ENABLED

|

||||

|

||||

/* ########################## Oscillator Values adaptation ####################*/

|

||||

/**

|

||||

* @brief Adjust the value of External High Speed oscillator (HSE) used in your application.

|

||||

* This value is used by the RCC HAL module to compute the system frequency

|

||||

* (when HSE is used as system clock source, directly or through the PLL).

|

||||

*/

|

||||

#if !defined (HSE_VALUE)

|

||||

#define HSE_VALUE 8000000U /*!< Value of the External oscillator in Hz */

|

||||

#endif /* HSE_VALUE */

|

||||

|

||||

#if !defined (HSE_STARTUP_TIMEOUT)

|

||||

#define HSE_STARTUP_TIMEOUT 100U /*!< Time out for HSE start up, in ms */

|

||||

#endif /* HSE_STARTUP_TIMEOUT */

|

||||

|

||||

/**

|

||||

* @brief Internal High Speed oscillator (HSI) value.

|

||||

* This value is used by the RCC HAL module to compute the system frequency

|

||||

* (when HSI is used as system clock source, directly or through the PLL).

|

||||

*/

|

||||

#if !defined (HSI_VALUE)

|

||||

#define HSI_VALUE 8000000U /*!< Value of the Internal oscillator in Hz*/

|

||||

#endif /* HSI_VALUE */

|

||||

|

||||

/**

|

||||

* @brief Internal Low Speed oscillator (LSI) value.

|

||||

*/

|

||||

#if !defined (LSI_VALUE)

|

||||

#define LSI_VALUE 40000U /*!< LSI Typical Value in Hz */

|

||||

#endif /* LSI_VALUE */ /*!< Value of the Internal Low Speed oscillator in Hz

|

||||

The real value may vary depending on the variations

|

||||

in voltage and temperature. */

|

||||

|

||||

/**

|

||||

* @brief External Low Speed oscillator (LSE) value.

|

||||

* This value is used by the UART, RTC HAL module to compute the system frequency

|

||||

*/

|

||||

#if !defined (LSE_VALUE)

|

||||

#define LSE_VALUE 32768U /*!< Value of the External oscillator in Hz*/

|

||||

#endif /* LSE_VALUE */

|

||||

|

||||

#if !defined (LSE_STARTUP_TIMEOUT)

|

||||

#define LSE_STARTUP_TIMEOUT 5000U /*!< Time out for LSE start up, in ms */

|

||||

#endif /* LSE_STARTUP_TIMEOUT */

|

||||

|

||||

/* Tip: To avoid modifying this file each time you need to use different HSE,

|

||||

=== you can define the HSE value in your toolchain compiler preprocessor. */

|

||||

|

||||

/* ########################### System Configuration ######################### */

|

||||

/**

|

||||

* @brief This is the HAL system configuration section

|

||||

*/

|

||||

#define VDD_VALUE 3300U /*!< Value of VDD in mv */

|

||||

#define TICK_INT_PRIORITY 15U /*!< tick interrupt priority (lowest by default) */

|

||||

#define USE_RTOS 0U

|

||||

#define PREFETCH_ENABLE 1U

|

||||

|

||||

#define USE_HAL_ADC_REGISTER_CALLBACKS 0U /* ADC register callback disabled */

|

||||

#define USE_HAL_CAN_REGISTER_CALLBACKS 0U /* CAN register callback disabled */

|

||||

#define USE_HAL_CEC_REGISTER_CALLBACKS 0U /* CEC register callback disabled */

|

||||

#define USE_HAL_DAC_REGISTER_CALLBACKS 0U /* DAC register callback disabled */

|

||||

#define USE_HAL_ETH_REGISTER_CALLBACKS 0U /* ETH register callback disabled */

|

||||

#define USE_HAL_HCD_REGISTER_CALLBACKS 0U /* HCD register callback disabled */

|

||||

#define USE_HAL_I2C_REGISTER_CALLBACKS 0U /* I2C register callback disabled */

|

||||

#define USE_HAL_I2S_REGISTER_CALLBACKS 0U /* I2S register callback disabled */

|

||||

#define USE_HAL_MMC_REGISTER_CALLBACKS 0U /* MMC register callback disabled */

|

||||

#define USE_HAL_NAND_REGISTER_CALLBACKS 0U /* NAND register callback disabled */

|

||||

#define USE_HAL_NOR_REGISTER_CALLBACKS 0U /* NOR register callback disabled */

|

||||

#define USE_HAL_PCCARD_REGISTER_CALLBACKS 0U /* PCCARD register callback disabled */

|

||||

#define USE_HAL_PCD_REGISTER_CALLBACKS 0U /* PCD register callback disabled */

|

||||

#define USE_HAL_RTC_REGISTER_CALLBACKS 0U /* RTC register callback disabled */

|

||||

#define USE_HAL_SD_REGISTER_CALLBACKS 0U /* SD register callback disabled */

|

||||

#define USE_HAL_SMARTCARD_REGISTER_CALLBACKS 0U /* SMARTCARD register callback disabled */

|

||||

#define USE_HAL_IRDA_REGISTER_CALLBACKS 0U /* IRDA register callback disabled */

|

||||

#define USE_HAL_SRAM_REGISTER_CALLBACKS 0U /* SRAM register callback disabled */

|

||||

#define USE_HAL_SPI_REGISTER_CALLBACKS 0U /* SPI register callback disabled */

|

||||

#define USE_HAL_TIM_REGISTER_CALLBACKS 0U /* TIM register callback disabled */

|

||||

#define USE_HAL_UART_REGISTER_CALLBACKS 0U /* UART register callback disabled */

|

||||

#define USE_HAL_USART_REGISTER_CALLBACKS 0U /* USART register callback disabled */

|

||||

#define USE_HAL_WWDG_REGISTER_CALLBACKS 0U /* WWDG register callback disabled */

|

||||

|

||||

/* ########################## Assert Selection ############################## */

|

||||

/**

|

||||

* @brief Uncomment the line below to expanse the "assert_param" macro in the

|

||||

* HAL drivers code

|

||||

*/

|

||||

/* #define USE_FULL_ASSERT 1U */

|

||||

|

||||

/* ################## Ethernet peripheral configuration ##################### */

|

||||

|

||||

/* Section 1 : Ethernet peripheral configuration */

|

||||

|

||||

/* MAC ADDRESS: MAC_ADDR0:MAC_ADDR1:MAC_ADDR2:MAC_ADDR3:MAC_ADDR4:MAC_ADDR5 */

|

||||

#define MAC_ADDR0 2U

|

||||

#define MAC_ADDR1 0U

|

||||

#define MAC_ADDR2 0U

|

||||

#define MAC_ADDR3 0U

|

||||

#define MAC_ADDR4 0U

|

||||

#define MAC_ADDR5 0U

|

||||

|

||||

/* Definition of the Ethernet driver buffers size and count */

|

||||

#define ETH_RX_BUF_SIZE ETH_MAX_PACKET_SIZE /* buffer size for receive */

|

||||

#define ETH_TX_BUF_SIZE ETH_MAX_PACKET_SIZE /* buffer size for transmit */

|

||||

#define ETH_RXBUFNB 8U /* 4 Rx buffers of size ETH_RX_BUF_SIZE */

|

||||

#define ETH_TXBUFNB 4U /* 4 Tx buffers of size ETH_TX_BUF_SIZE */

|

||||

|

||||

/* Section 2: PHY configuration section */

|

||||

|

||||

/* DP83848_PHY_ADDRESS Address*/

|

||||

#define DP83848_PHY_ADDRESS 0x01U

|

||||

/* PHY Reset delay these values are based on a 1 ms Systick interrupt*/

|

||||

#define PHY_RESET_DELAY 0x000000FFU

|

||||

/* PHY Configuration delay */

|

||||

#define PHY_CONFIG_DELAY 0x00000FFFU

|

||||

|

||||

#define PHY_READ_TO 0x0000FFFFU

|

||||

#define PHY_WRITE_TO 0x0000FFFFU

|

||||

|

||||

/* Section 3: Common PHY Registers */

|

||||

|

||||

#define PHY_BCR ((uint16_t)0x00) /*!< Transceiver Basic Control Register */

|

||||

#define PHY_BSR ((uint16_t)0x01) /*!< Transceiver Basic Status Register */

|

||||

|

||||

#define PHY_RESET ((uint16_t)0x8000) /*!< PHY Reset */

|

||||

#define PHY_LOOPBACK ((uint16_t)0x4000) /*!< Select loop-back mode */

|

||||

#define PHY_FULLDUPLEX_100M ((uint16_t)0x2100) /*!< Set the full-duplex mode at 100 Mb/s */

|

||||

#define PHY_HALFDUPLEX_100M ((uint16_t)0x2000) /*!< Set the half-duplex mode at 100 Mb/s */

|

||||

#define PHY_FULLDUPLEX_10M ((uint16_t)0x0100) /*!< Set the full-duplex mode at 10 Mb/s */

|

||||

#define PHY_HALFDUPLEX_10M ((uint16_t)0x0000) /*!< Set the half-duplex mode at 10 Mb/s */

|

||||

#define PHY_AUTONEGOTIATION ((uint16_t)0x1000) /*!< Enable auto-negotiation function */

|

||||

#define PHY_RESTART_AUTONEGOTIATION ((uint16_t)0x0200) /*!< Restart auto-negotiation function */

|

||||

#define PHY_POWERDOWN ((uint16_t)0x0800) /*!< Select the power down mode */

|

||||

#define PHY_ISOLATE ((uint16_t)0x0400) /*!< Isolate PHY from MII */

|

||||

|

||||

#define PHY_AUTONEGO_COMPLETE ((uint16_t)0x0020) /*!< Auto-Negotiation process completed */

|

||||

#define PHY_LINKED_STATUS ((uint16_t)0x0004) /*!< Valid link established */

|

||||

#define PHY_JABBER_DETECTION ((uint16_t)0x0002) /*!< Jabber condition detected */

|

||||

|

||||

/* Section 4: Extended PHY Registers */

|

||||

#define PHY_SR ((uint16_t)0x10U) /*!< PHY status register Offset */

|

||||

|

||||

#define PHY_SPEED_STATUS ((uint16_t)0x0002U) /*!< PHY Speed mask */

|

||||

#define PHY_DUPLEX_STATUS ((uint16_t)0x0004U) /*!< PHY Duplex mask */

|

||||

|

||||

/* ################## SPI peripheral configuration ########################## */

|

||||

|

||||

/* CRC FEATURE: Use to activate CRC feature inside HAL SPI Driver

|

||||

* Activated: CRC code is present inside driver

|

||||

* Deactivated: CRC code cleaned from driver

|

||||

*/

|

||||

|

||||

#define USE_SPI_CRC 0U

|

||||

|

||||

/* Includes ------------------------------------------------------------------*/

|

||||

/**

|

||||

* @brief Include module's header file

|

||||

*/

|

||||

|

||||

#ifdef HAL_RCC_MODULE_ENABLED

|

||||

#include "stm32f1xx_hal_rcc.h"

|

||||

#endif /* HAL_RCC_MODULE_ENABLED */

|

||||

|

||||

#ifdef HAL_GPIO_MODULE_ENABLED

|

||||

#include "stm32f1xx_hal_gpio.h"

|

||||

#endif /* HAL_GPIO_MODULE_ENABLED */

|

||||

|

||||

#ifdef HAL_EXTI_MODULE_ENABLED

|

||||

#include "stm32f1xx_hal_exti.h"

|

||||

#endif /* HAL_EXTI_MODULE_ENABLED */

|

||||

|

||||

#ifdef HAL_DMA_MODULE_ENABLED

|

||||

#include "stm32f1xx_hal_dma.h"

|

||||

#endif /* HAL_DMA_MODULE_ENABLED */

|

||||

|

||||

#ifdef HAL_ETH_MODULE_ENABLED

|

||||

#include "stm32f1xx_hal_eth.h"

|

||||

#endif /* HAL_ETH_MODULE_ENABLED */

|

||||

|

||||

#ifdef HAL_CAN_MODULE_ENABLED

|

||||

#include "stm32f1xx_hal_can.h"

|

||||

#endif /* HAL_CAN_MODULE_ENABLED */

|

||||

|

||||

#ifdef HAL_CAN_LEGACY_MODULE_ENABLED

|

||||

#include "Legacy/stm32f1xx_hal_can_legacy.h"

|

||||

#endif /* HAL_CAN_LEGACY_MODULE_ENABLED */

|

||||

|

||||

#ifdef HAL_CEC_MODULE_ENABLED

|

||||

#include "stm32f1xx_hal_cec.h"

|

||||

#endif /* HAL_CEC_MODULE_ENABLED */

|

||||

|

||||

#ifdef HAL_CORTEX_MODULE_ENABLED

|

||||

#include "stm32f1xx_hal_cortex.h"

|

||||

#endif /* HAL_CORTEX_MODULE_ENABLED */

|

||||

|

||||

#ifdef HAL_ADC_MODULE_ENABLED

|

||||

#include "stm32f1xx_hal_adc.h"

|

||||

#endif /* HAL_ADC_MODULE_ENABLED */

|

||||

|

||||

#ifdef HAL_CRC_MODULE_ENABLED

|

||||

#include "stm32f1xx_hal_crc.h"

|

||||

#endif /* HAL_CRC_MODULE_ENABLED */

|

||||

|